SDH technology solve the existing limitations of PDH. It was the beginning of best technology in the telecom sector. Before 1970 most of the worlds telephony system were based on single line, voice frequency, connections over twisted copper pair. But there was a change in telecom sector very fast & it was replaced by SDH system. SDH technology was a new revolution in the telecom sector.

Origins Of SDH

The first of the working systems to be introduced was the SYNTRAN (Synchronous Transmission) system from Bellcore. This did not live up to expectations and was soon replaced with SONET (Synchronous Optical Network).

Initially SONET could only carry the ANSI (American National Standards Institute) bit rates i.e. 1.5, 6, 45 Mbit/s.Since the aim of the project was to provide easier international interconnection, SONET was modified to carry the European standard bit rates of 2, 8, 34 & 140 Mbit/s.

In 1989 CCITT (Consultative Committee International for Telephone and Telegraph), now ITU-T (International Telecommunications Union - Telecommunication's standardisation section) published recommendations G704, G.707, G.708 and G.709 which covered the standards for SDH.

These were adopted in North America by ANSI (SONET is now thought of as a subset of SDH), making SDH a truly global standard.

⏩SDH permits the mixing of existing European (ETSI) and North American (ANSI) PDH bit rates.

⏩SDH is apparently synchronous. All SDH equipment is based on the use of a single master reference clock source.

⏩Compatible with the majority of existing PDH bit rates

⏩SDH provides for much simpler extraction/insertion, of a lower order bit rate from a higher order aggregate stream, without the need to de-multiplex in stages.

⏩SDH provides cross-connection of any low order stream to any other low order stream without the need to de-multiplex in stages.

⏩SDH allows for integrated management and performance monitoring using a centralised network control.

⏩SDH provides for a standard optical interface thus allowing the inter-working of different manufacturers equipment's.

⏩SDH provides for future higher order rates by a simple BYTE interleaving process.

⏩SDH standards have been prepared for future applications such as Asynchronous Transfer Mode (ATM), High Definition Television (HDTV) and Metropolitan Area Networks (MAN).

⏩Increase in system reliability due to reduction of necessary equipment/jumpering.

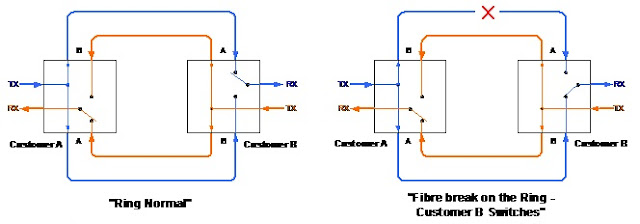

SDH networks are usually deployed in rings. This has the advantage of giving protection to the data, by providing an alternate route for it to travel over in the event of equipment or network failure.

Each side of the ring (known as A and B, or sometimes, East and West), consists of an individual transmit and receive fiber. These fiber will take diverse physical paths to the distant end equipment to minimize the risk of both routes failing at the same time. The SDH equipment can detect when there is a problem and will automatically switch to the alternate route.

To speed up switching times, the SDH multiplexers transmit on both routes simultaneously, but only elect to receive on one side. This means that only the receiving end needs to switch (the transmitting end stays the same), thus reducing the impact of a fault on the customers' data. To further improve switching times, each network element will switch independently of its neighbors (Uni-directional). This means that if a single fiber is broken, only one site needs to switch.

SDH Principles

Each container then has some control information known as the 'Path Overhead' (POH) added to it. The path overhead bytes allow the system operator to achieve end to end path monitoring of areas such as error indication, alarm indication and performance monitoring data. Together the container and the path overhead form a 'Virtual Container' (VC).

In an SDH network, all equipment is synchronised from a single master clock.The timing of the PDH signals entering the SDH network and being mapped into the VC's may vary slightly in frequency and/or phase from the SDH master clock. Additional stuffing bits are either added, or used as data bits, to align the different clock rates in a process called Justification.

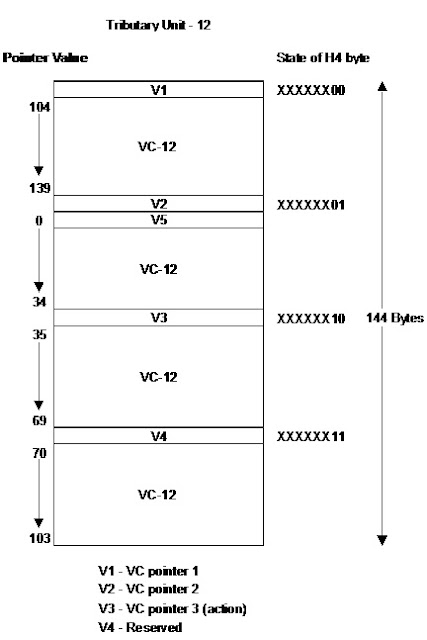

Groups of four VC frames make up an SDH multiframe. Due to clock phase differences, the start of the multiframe may not coincide with the start of the four VC frames and as a result, the location of individual virtual containers within the multiframe may vary. Identification of the start of the four VC's is achieved by adding a 'Pointer' that identifies the start of the VC within the multiframe. The VC and its relevant pointer together form a 'Tributary Unit' (TU).

Tributary units are then multiplexed together in stages (Tributary User Group 2 (TUG-2) Tributary User Group 3 (TUG-3) - Virtual Container 4 (VC-4)), to form an Administrative Unit 4 (AU-4). Additional stuffing, pointers and overheads are added during this procedure. This AU-4 in effect contains 63 x 2 Mbit/s channels and all the control information that is required.

Finally, Section Overheads (SOH) are added to the AU-4. These SOH's contain the control bytes for the STM-1 section comprising of framing, section performance monitoring, maintenance and operational control information. An AU-4 plus its SOH's together form an STM-1 transport frame.

STM Hierarchy and Container Bit Rates

The first hierarchy level for SDH is set at 155,520 kbit/s/s.

This is known as a Synchronous Transport Module 1 (STM-1). Higher levels are simply multiples of the first level, which are denoted by the number after the-

At present the SDH hierarchy is as follows:

➤STM-1: 155,520 kbit/s. (155 Mbit/s)

➤STM-4: 622,080 kbit/s. (620 Mbit/s)

➤STM-16: 2,488,320 kbit/s. (2.5 Gbit/s)

➤STM-64: 9,953,280 kbit/s. (10 Gbit/s)

The diagram shows the complete SDH multiplexing structure. PDH signals enter on the right into the relevant container and progress across to the left through the various processes.

The route via VC-3 and AU-3 (shown with dotted lines) are for SONET applications (does not include 140 Mbit/s payloads), and are not applicable in Europe.

Graphical SDH Multiplexing Structure

SDH Structure Details

SDH Concatenation

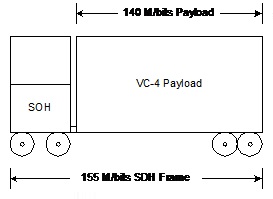

The SDH frame can be thought of as an articulated lorry. The data to be transported is placed in the VC-4 'Container'. This is then hitched to the SOH 'Cab unit' that 'drives' the data to its destination.

The maximum carrying capacity of the vehicle is determined by the size of the 'container'. Therefore although the SDH signal is 155 Mbit/s in size, the largest single circuit that can be transmitted at any one time by the customer is limited to the size of the VC-4 i.e. 140 Mbit/s.

When using higher rates of SDH (STM-4, STM-16 etc), multiple 'containers' and 'cabs' are added one after another, to form a bigger vehicle. The customer is still limited to a single circuit size of 140 Mbit/s however, because each individual 'container' is the same size (140 Mbit/s). They can however transmit multiple 140 Mbit/s circuits simultaneously. The diagram below represents the standard STM-4 structure.

This limitation of 140 Mbit/s per individual circuit is not a particularly efficient way of managing bandwidth and a method of combining 'containers' together has been developed which is called 'Concatenation'.

The diagram above represents an STM-4 concatenated structure (VC-4-4C).

Concatenated paths are commonly defined as VC-4-xC circuits (where x is size of the concatenation).

➥STM-4 concatenation (written as VC-4-4c), provides a single circuit with a bit rate of approximately 600M (actually 599.04 Mbit/s)

➥STM-16 concatenation (written as VC-4-16c), provides a single circuit with a bit rate of approximately 2.2G (actually 2.2396160 Gbit/s)

➥STM-64 concatenation (written as VC-4-64c), provides a single circuit with a bit rate of approximately 10G (actually 9.584640 Gbit/s)

➥STM-256 concatenation (written as VC-4-256c), provides a single circuit with a bit rate of approximately 38G (actually 38.338560 Gbit/s).

SDH Functional Details

Mapping of a C-12 into a VC-12

The mapping of a C-12 into a VC-12 is not done on an individual C-12 basis. The mapping process includes the addition of fixed stuffing, overhead bytes and justification. This process takes place over 4 C-12's. These four C-12's plus stuffing and overheads make up a VC-12 Multiframe.

Frame number One has two bytes of fixed stuffing added to it. One byte is added at the start and one byte at the end. It then has one byte of overhead control information added to the start. This byte of over head is called the V5 byte and is known as the Path OverHead (POH).

Frame number Two has two bytes of fixed stuffing added to it. One byte is added at the start and one byte at the end. It then has one byte of overhead control information added to the start. This control byte in frame 2 is the Lower Order Path Trace or J2 byte. J2 is used to check continuity of a 2 Mbit/s path. It is currently not supported by manufacturers

Frame number Three has two bytes of fixed stuffing added to it. One byte is added at the start and one byte at the end. It then has one byte of overhead control information added to the start. This control byte N2, in frame 3 is called the Network Operator or Tandem Control byte. N2 is used to transmit performance-monitoring information where the circuit spans differing vendors networks.

Frame number Four has one byte of fixed stuffing added to the end. It also has one byte of variable stuffing added to the start. It then has one byte of overhead control information added to the start. This control byte in frame 4 is called K4.

Bits 1 to 4 of K4 are used for 2 Mbit/s Automatic Protection Switching or APS. APS is used to automatically switch a single 2 Mbit/s circuit to its alternate path if a fault condition occurs.

S1 and S2 in frame 4 provide the justification opportunity. Justification is the process that compensates for clock frequency differences between the incoming PDH signal and the SDH master clock.

Under ideal conditions S1 is used for stuffing and S2 is used for data.

S2 can be used to provide extra stuffing if the PDH signal is slow.

S1 can be used to provide extra data bits if the PDH signal is fast. The C1 and C2 bits in frames 2,3 and 4 of the multiframe control S1 and S2 respectively. Because each individual frame may or may not need justification, majority rule determines the use of S1 and S2.

An incoming PDH 2 Mbit/s signal has a maximum permitted clock deviation of 50 parts per million (ppm). This means the PDH signal should waver by no more than 100 bits in either direction, giving a spread of 200 bits.

SDH provides for 1 bit of justification (either stuffing or data), every VC-12 multiframe. As there are 2000 multiframes per second this gives a compensation spread of 2000 bits which is more than adequate compared to the 200 bits permitted by PDH.

BIP-2 is Bit Interleaved Parity Check-2. This looks at the data in the C-12. It counts all of the binary one's that it sees in the odd positions (i.e. bits 1,3,5,7 etc). If this count is an even number it puts a binary 0 in bit 1 of V5. If this count is an odd number it puts a binary 1 in bit 1 of V5.

V1 and V2 bytes in the TU-12 together form the pointer to the start of V5. The value of V1 and V2 is a count of the number of bytes from the end of V2 to the start of the V5 byte. This count does not include V1, V2, V3 or V4.

Because V5 can actually start anywhere within the TU multiframe, this pointer value ranges from 0 to 139. An example is shown below:

When the 2 Mbit/s port is first cross-connected on the multiplexer and an end to end path is created, a value for the initial pointer will be generated, and placed in the V1 and V2 bytes.

If a fault causes a break in the transmission path it could result in a change of V5 position. This change needs to be transmitted to the distant end. If this is the case a new pointer value will be generated.

The old pointer value is then incremented/decremented in steps, by a value of one each time, until it matches the new value required.

V1 and V2 bytes are shown below:

New Data Flag - the normal value of the new data flag is '0110. If a change of pointer value

is needed, these bits will change to 1001, indicating to the distant end that the 10-bit pointer value has been changed.

Multiplexing of TU-12 into a TUG-2

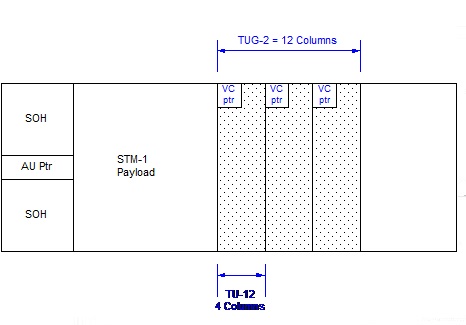

Each VC-12 consists of 144 bytes of information. Each frame has 36 bytes. These 36 bytes fill up exactly 4 columns of the STM-1 frame. 3 separate TU-12's are directly mapped together to form a TUG-2.

Under ideal conditions the 3 TU-12's will fit exactly into 12 columns of the STM-1 frame as shown below:

If the timing of a VC causes it to slip with respect to the timing of the TUG, the pointer is adjusted to indicate the new alignment The location of the pointer is fixed within the TUG-2 regardless of the position of the VC.

Mapping of a TUG-3 into a VC-4 signal

The function of the bytes is as follows:

The RFI bits are used to report back to the distant end, the results of the BIP-8 check. This field has four bits with a total of eight values. If the BIP-8 check failed on the 'bit 1' count a value of 0001 is used. If it failed on the 'bit 2' check a value of 0010 is used. 'Bit 3', 0011 etc. This alarm is also known as HO FEBE or High Order Far End Bit Errors.

The RDI field is used to indicate to the distant end that the multiplexer has an alarm condition (such as received path AIS in H1/H2, or loss of signal). In effect a loss of VC-4 frame alignment alarm.

A binary 1 in this field indicates an alarm condition; a binary 0 indicates normality. This alarm is also known as HO FERF or High Order Far End Receiver Failure. The remaining three bits are spare.

Mapping of a VC-4 into an STM-1 frame

An AU pointer is added to the VC-4 to form an AU-4 or Administrative Unit -4. This pointer shows the phase alignment of the VC-4 with respect to the STM-1 frame. The AU pointers are in a fixed position within the STM-1 frame and are used to show the location of the first byte of the VC-4 POH, and also to provide a justification opportunity for VC-4 (140Mbit/s) payloads.

The AU-4 is then mapped directly into an AUG or Administrative Unit Group, which then has the Section Overheads or SOH, added to it. These section overheads provide STM-1 framing, section performance monitoring and other maintenance functions pertaining to the section path. The VC-4 payload, plus AU pointers and Section Overheads, together form the complete STM-1 transport frame.

AU Pointers

Because SDH can accept PCM signals at 140 Mbit/s directly into a VC-4 container there needs to be a mechanism to compensate for clock discrepancies between the SDH and PDH networks. The principles governing AU/VC-4 justification are identical to those of the lower order VC-12 signals. This justification process means that the VC-4 payload can move within the STM-1 frame format; therefore pointers are required to indicate the start of the VC-4.

The AU pointer bytes are part of the STM-1 section overheads and comprise of H1 and H2 as pointer indicators and H3 as the negative justification opportunity.

The H bytes are in multiples of three (to take into account AU-3 SONET mapping), but only the first byte of both the H1 and H2 bytes are used at VC-4 and the second and third bytes set to a null pointer indicator (NPI), a fixed bit pattern.

The pointer value is the offset between the end of the H3 byte and the start of the VC-4 POH i.e. from the end of H3 to the start of the J1 byte.

Because J1 can be anywhere (in-groups of three to take into account AU-3 SONET mapping), within the STM-1 payload area this AU pointer value can range from 0 to 782. The multiplexer will attempt to place the VC-4 frame at pointer value 522. This will fit the VC-4 directly into the STM-1 frame. There are occasions where due to justification processes the VC-4 will span across STM-1 frames.

VC-4 Justification

As SDH caters for customer input rates of 140Mbit/s directly some form of justification is needed at the VC-4 level. This is achieved by using the 3 bytes of H3 and the next 3 bytes immediately following H3.

The justification takes place in frame number 3, of a 4 frame multiframe. Justification control is via a buffer system (as opposed to the control bits (C1, C2) in VC-12 justification). The incoming data is fed into a buffer. This buffer has two threshold levels. A 'low fill' level for slow rates and a 'high fill' threshold for fast data. When these thresholds are met, the H3 bytes and the 3 bytes immediately following are set accordingly.

If the customer data is being received at a faster rate than normal, the 3 bytes of H3 are used for customer data. This is known as negative justification.

If the customer data is being received at a slower rate than normal, the 3 bytes immediately following H3 are used for padding. This is known as Positive justification.

B1 - Byte Interleaved Parity Check 8 (BIP-8). This byte provides an error monitoring function for the entire STM-1 frame after scrambling (2B1Q). It checks every bit in the STM-1 frame. It looks at every 'bit1' in the frame and counts the number of binary 1's. If this number is even, a binary 0 is placed in the first bit of the BIP-8 byte. If the result of the count is an odd number of binary 1's, a binary 1 is placed in the first bit of the BIP-8 byte. The sequence is then repeated for all of the bit 2's in the frame, with the corresponding result being placed in the second bit of the BIP-8 byte. This continues with bit 3's in the third bit, bit 4's in the forth bit, etc until the entire STM-1 frame has been checked.

F1 – Maintenance Channel. This byte is used to convey back to the distant end a count of any errors detected by the BIP-8 error check in byte B1.

D1 to D3 - Data Communications Channel (DCC). These 3 bytes provide a 192 kbit/s data channel for the use of network management systems.

A comparison between the BIP-8 and BIP-24 checks reveal if there were any scrambling errors (2B1Q).

S1 - Synchronisation Status Message. Bits 5, 6, 7 and 8 of the S1 byte provide a quality indication of the received clock synchronisation signal.

0000 - indicates a quality unknown message.

0010 - indicates a G.811 Primary reference clock with an error rate of greater than 1x10-11 per day.

In 1989 CCITT (Consultative Committee International for Telephone and Telegraph), now ITU-T (International Telecommunications Union - Telecommunication's standardisation section) published recommendations G704, G.707, G.708 and G.709 which covered the standards for SDH.

Features and Advantages of SDH

⏩SDH permits the mixing of existing European (ETSI) and North American (ANSI) PDH bit rates.

⏩SDH is apparently synchronous. All SDH equipment is based on the use of a single master reference clock source.

⏩Compatible with the majority of existing PDH bit rates

⏩SDH provides for much simpler extraction/insertion, of a lower order bit rate from a higher order aggregate stream, without the need to de-multiplex in stages.

⏩SDH provides cross-connection of any low order stream to any other low order stream without the need to de-multiplex in stages.

⏩SDH allows for integrated management and performance monitoring using a centralised network control.

⏩SDH provides for a standard optical interface thus allowing the inter-working of different manufacturers equipment's.

⏩SDH provides for future higher order rates by a simple BYTE interleaving process.

⏩SDH standards have been prepared for future applications such as Asynchronous Transfer Mode (ATM), High Definition Television (HDTV) and Metropolitan Area Networks (MAN).

⏩Increase in system reliability due to reduction of necessary equipment/jumpering.

Basic SDH Network Topology

Each side of the ring (known as A and B, or sometimes, East and West), consists of an individual transmit and receive fiber. These fiber will take diverse physical paths to the distant end equipment to minimize the risk of both routes failing at the same time. The SDH equipment can detect when there is a problem and will automatically switch to the alternate route.

|

| Basic SDH System |

The SDH standard defines a number of 'Containers' each corresponding to an existing PDH bit rate. Information from the incoming PDH signal is mapped into the relevant container. This is achieved using a bit stuffing procedure similar to that used in a PDH multiplexer.

The first hierarchy level for SDH is set at 155,520 kbit/s/s.

This is known as a Synchronous Transport Module 1 (STM-1). Higher levels are simply multiples of the first level, which are denoted by the number after the-

At present the SDH hierarchy is as follows:

➤STM-1: 155,520 kbit/s. (155 Mbit/s)

➤STM-4: 622,080 kbit/s. (620 Mbit/s)

➤STM-16: 2,488,320 kbit/s. (2.5 Gbit/s)

➤STM-64: 9,953,280 kbit/s. (10 Gbit/s)

SDH allows for various PDH input rates to be mapped into containers as shown below:

➤Container C11: 1544 kbit/s (1.5 Mbit/s)

➤Container C12: 2048 kbit/s (2 Mbit/s)

➤Container C2: 6312 kbit/s (6 Mbit/s)

➤Container C3: 49,536 kbit/s (45 & 34 Mbit/s)

➤Container C4: 139,264 kbit/s (140 Mbit/s)

Full SDH Multiplexing Structure

The route via VC-3 and AU-3 (shown with dotted lines) are for SONET applications (does not include 140 Mbit/s payloads), and are not applicable in Europe.

|

| SDH Frame |

|

| SDH Frame |

STM-1 Frame Structure

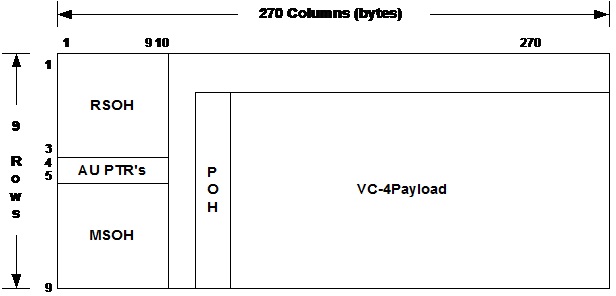

The STM-1 transport frame has a duration of 125ms. It contains 2430 bytes of information. Each byte contains 8 data bits (i.e. a 64kbit/s channel).

The number of frames per second is 1 second / 125ms = 8000 Frames per second.

Therefore the rate transmitted to line is: -

8 bits x 2430 bytes x 8000 per second = 155,520,000 bits/s or 155 Mbit/s.

As each frame consists of 2430 bytes, this would prove very difficult to show as a diagram on a page. To get round this, we show the frame chopped up into 9 segments, stacked on top of each other as shown in the diagram below.

The bits start at the top left with byte number one and are read from left to right and top to bottom. They are arranged as 270 columns across and 9 rows down.

Therefore byte 270 is the byte in column 270, row 1. Byte 271 is in column 1, row 2 and byte 2430 is located at column 270, row 9 etc.

The STM-1 transport frame has a duration of 125ms. It contains 2430 bytes of information. Each byte contains 8 data bits (i.e. a 64kbit/s channel).

The number of frames per second is 1 second / 125ms = 8000 Frames per second.

Therefore the rate transmitted to line is: -

8 bits x 2430 bytes x 8000 per second = 155,520,000 bits/s or 155 Mbit/s.

As each frame consists of 2430 bytes, this would prove very difficult to show as a diagram on a page. To get round this, we show the frame chopped up into 9 segments, stacked on top of each other as shown in the diagram below.

The bits start at the top left with byte number one and are read from left to right and top to bottom. They are arranged as 270 columns across and 9 rows down.

Therefore byte 270 is the byte in column 270, row 1. Byte 271 is in column 1, row 2 and byte 2430 is located at column 270, row 9 etc.

|

| SDH Frame |

The SDH frame can be thought of as an articulated lorry. The data to be transported is placed in the VC-4 'Container'. This is then hitched to the SOH 'Cab unit' that 'drives' the data to its destination.

|

| VC-4 in STM-1 |

|

| VC-4-4C in STM-4 |

The diagram above represents an STM-4 concatenated structure (VC-4-4C).

➥STM-4 concatenation (written as VC-4-4c), provides a single circuit with a bit rate of approximately 600M (actually 599.04 Mbit/s)

➥STM-16 concatenation (written as VC-4-16c), provides a single circuit with a bit rate of approximately 2.2G (actually 2.2396160 Gbit/s)

➥STM-64 concatenation (written as VC-4-64c), provides a single circuit with a bit rate of approximately 10G (actually 9.584640 Gbit/s)

➥STM-256 concatenation (written as VC-4-256c), provides a single circuit with a bit rate of approximately 38G (actually 38.338560 Gbit/s).

Mapping of a 2 Mbit/s PDH signal into a C-12.

The 2 Mbit/s PDH input signal is mapped into a Container 12 (C-12). The input frame consists of 32 bytes of information and this fits directly into the C-12.

|

| V5 byte |

Frame number Three has two bytes of fixed stuffing added to it. One byte is added at the start and one byte at the end. It then has one byte of overhead control information added to the start. This control byte N2, in frame 3 is called the Network Operator or Tandem Control byte. N2 is used to transmit performance-monitoring information where the circuit spans differing vendors networks.

Bits 1 to 4 of K4 are used for 2 Mbit/s Automatic Protection Switching or APS. APS is used to automatically switch a single 2 Mbit/s circuit to its alternate path if a fault condition occurs.

Under ideal conditions S1 is used for stuffing and S2 is used for data.

S2 can be used to provide extra stuffing if the PDH signal is slow.

S1 can be used to provide extra data bits if the PDH signal is fast. The C1 and C2 bits in frames 2,3 and 4 of the multiframe control S1 and S2 respectively. Because each individual frame may or may not need justification, majority rule determines the use of S1 and S2.

SDH provides for 1 bit of justification (either stuffing or data), every VC-12 multiframe. As there are 2000 multiframes per second this gives a compensation spread of 2000 bits which is more than adequate compared to the 200 bits permitted by PDH.

The diagram below shows the complete VC-12 multiframe:

The VC-12 multiframe contains a total of 140 bytes and duration of 500ms

V5 Path Overhead (TU-12 POH)

The V5 byte is constructed as shown below: |

| SDH VC-12 Multiframe |

|

| SDH V5 |

It then counts all of the binary one's that it sees in the even positions of the C-12 (i.e. bits 2,4,6,8 etc). If this count is an even number it puts a binary 0 in bit 2 of V5. If this count is an odd number it puts a binary 1 in bit 2 of V5.

This BIP-2 is then recalculated at the distant end. If the count is different, then some bit corruption has occurred.

FEBE is Far End Bit errors. This bit is set correspondingly to the result of the BIP-2 check. If errors are received at the distant end then there needs to be a mechanism for informing the sender of the problem. If bit 3 of the V5 is a binary 0 then BIP-2 was ok. If bit 3 of the V5 is a binary 1 then BIP-2 was bad and the transmitting end will raise an alarm.

FEBE alarm is also known as Remote Error Indication (REI). The term 'Far End Bit errors' tends to imply that the fault is at the remote end. It could actually be from many different places in the route, so the name has been changed to make it less ambiguous.

RFI is Remote Failure Indicator. If a Loss of Pointer and/or AIS all 1's in V1/V2) is detected in the receive path, a binary 1 is sent back in bit 4 of V5. In effect a loss of TU-12 frame alignment alarm.This alarm is also known as RAI or Remote Alarm Indication.

LO Sig. Label is Lower order Signal Label. This is used to indicate the type of VC payload. It comprises of bits 5, 6 and 7 of V5, but only 2 are actually needed.

000 - indicates the port is unequipped. 010 - indicates that it is asynchronously mapped i.e. normal, in service.

On some manufacturers equipment this determines if alarms are raised when a 2 Mbit/s port is physically disconnected.

FERF is Far End Receiver Fail. Bit 8 in V5 is set to binary 1 if the distant end has detected certain TU path alarms. This alarm is also known as RDI or Remote Defect Alarm.

Mapping of a VC-12 into a TU-12 signal

The V5 byte must be seen by the distant end for it to detect the start of the multiframe, (similar to the use of the multiframe alignment word in PDH), and hence the start of the 2 Mbit/s signal. There must be some mechanism therefore to ensure that the distant end can detect V5.

This is achieved by adding four overhead bytes to the multiframe, which together form a calculated byte count to the start of V5. This is called a pointer value and is known as the TU Pointer.

There are four pointer bytes called V1, V2, V3 and V4. Only V1 and V2 are actually needed to calculate the location of V5.

TU Pointers

The V5 byte must be seen by the distant end for it to detect the start of the multiframe, (similar to the use of the multiframe alignment word in PDH), and hence the start of the 2 Mbit/s signal. There must be some mechanism therefore to ensure that the distant end can detect V5.

This is achieved by adding four overhead bytes to the multiframe, which together form a calculated byte count to the start of V5. This is called a pointer value and is known as the TU Pointer.

There are four pointer bytes called V1, V2, V3 and V4. Only V1 and V2 are actually needed to calculate the location of V5.

|

| V1,V2,V3 and V4 |

V1 and V2 bytes in the TU-12 together form the pointer to the start of V5. The value of V1 and V2 is a count of the number of bytes from the end of V2 to the start of the V5 byte. This count does not include V1, V2, V3 or V4.

Because V5 can actually start anywhere within the TU multiframe, this pointer value ranges from 0 to 139. An example is shown below:

|

| Example of TU pointers details |

When the 2 Mbit/s port is first cross-connected on the multiplexer and an end to end path is created, a value for the initial pointer will be generated, and placed in the V1 and V2 bytes.

If a fault causes a break in the transmission path it could result in a change of V5 position. This change needs to be transmitted to the distant end. If this is the case a new pointer value will be generated.

The old pointer value is then incremented/decremented in steps, by a value of one each time, until it matches the new value required.

V1 and V2 bytes are shown below:

|

| V1 and V2 Bytes |

is needed, these bits will change to 1001, indicating to the distant end that the 10-bit pointer value has been changed.

TU Type - these two bits are set to '10' to indicate that the multiframe is carrying a TU-12 (2 Mbit/s) payload.

A value of 00 indicates a TU-2 (6 Mbit/s) payload.

A value of 11 indicates a TU-11 (1.5 Mbit/s) payload.

I and D bits are used to increment and decrements the existing pointer value, by inverting the bits as necessary.

Each VC-12 consists of 144 bytes of information. Each frame has 36 bytes. These 36 bytes fill up exactly 4 columns of the STM-1 frame. 3 separate TU-12's are directly mapped together to form a TUG-2.

|

| TU-12 into a TUG-2 |

If the timing of a VC causes it to slip with respect to the timing of the TUG, the pointer is adjusted to indicate the new alignment The location of the pointer is fixed within the TUG-2 regardless of the position of the VC.

Mapping of a TUG-2 into a TUG-3 signal

The mapping of TUG-2's into TUG-3's uses fixed byte interleaving and is shown below. The inclusion of the TUG-3 level is primarily to provide a structure for direct 34Mbit/s and 45Mbit/s input rates.The 'Null Pointer Indicator' (NPI), is used to distinguish between TUG-3's which carry TUG-2's (2megs), and TUG-3's which carry VC-3 (34/45 Mbit/s) payloads.

The NPI consists of the first 3 bytes of the first column of each TUG-3. The remaining bytes of this column and the entire second column are stuffing.Each TUG-3 consists of 86 columns of information.

The mapping of TUG-2's into TUG-3's uses fixed byte interleaving and is shown below. The inclusion of the TUG-3 level is primarily to provide a structure for direct 34Mbit/s and 45Mbit/s input rates.The 'Null Pointer Indicator' (NPI), is used to distinguish between TUG-3's which carry TUG-2's (2megs), and TUG-3's which carry VC-3 (34/45 Mbit/s) payloads.

The NPI consists of the first 3 bytes of the first column of each TUG-3. The remaining bytes of this column and the entire second column are stuffing.Each TUG-3 consists of 86 columns of information.

|

| TUG-2 into TUG-3 |

SDH provides for fixed mapping from TUG-3 into a VC-4 container as shown in the diagram.The three TUG-3's are byte interleaved to form the VC-4 payload. At this point two columns of fixed stuffing are added and the 'VC-4 Path Overhead' is added to the start. These bytes together form the VC-4, which is 261 columns long.

VC-4 Path Overhead

|

| TUG-3 into VC-4 |

The VC-4 Path Overhead consists of one whole column of nine bytes as shown below. It forms the start of the VC-4 payload area. The POH contains control and status messages (similar to the V5 byte) at the higher order.

|

| VC-4 Details in SDH |

J1 - Higher Order Path trace. This byte is used to provide a fixed length user configurable string, which can be used to verify network topology connections. It is not supported by all manufactures.

B3 - Bit Interleaved Parity Check (BIP-8). This byte provides an error monitoring function for the VC-4 payload.

It checks every bit in the VC-4 payload (not the POH). It looks at every 'bit1' in the payload and counts the number of binary 1's. If this number is even, a binary 0 is placed in the first bit of the BIP-8 byte. If the result of the count is an odd number of binary 1's, a binary 1 is placed in the first bit of the BIP-8 byte.

This sequence is then repeated for all of the bit 2's in the payload, with the corresponding result being placed in the second bit of the BIP-8 byte. This continues with bit 3's in the third bit, bit 4's in the forth bit, etc until the entire VC-4 payload is checked.

C2 - Higher Order Signal Label. (Container Composition). This byte indicates the composition of the VC-4 payload. A value of 0000 0010 indicates the VC-4 is carrying TUG structured data i.e. TUG-3’s. A value of 0001 0010 indicates the VC-4 is carrying a C-4 i.e. a customers 140 Mbit/s PDH signal.

G1 - Higher Order Path Status. This byte is used to transmit path status information back to the distant end. It consists of 'RFI' and 'RDI' bits.

A binary 1 in this field indicates an alarm condition; a binary 0 indicates normality. This alarm is also known as HO FERF or High Order Far End Receiver Failure. The remaining three bits are spare.

F2 -Path User Channel. This byte provides for a user communication channel.

H4 - Multiframe Indicator. In VC mapping this byte indicates which frame of the multiframe is being transmitted (1 to 4).

Z3 -Path User Channel. This byte provides for a user communication channel.

K3 -Automatic protection Switching (APS). Bits 1 to 4 provide for automatic protection switching control with VC-4 payloads. Bits 5 to 8 are spare.

N1 - Tandem Connection monitoring. N1 is used to supply performance-monitoring data between the ends of a circuit that spans differing vendors.

An AU pointer is added to the VC-4 to form an AU-4 or Administrative Unit -4. This pointer shows the phase alignment of the VC-4 with respect to the STM-1 frame. The AU pointers are in a fixed position within the STM-1 frame and are used to show the location of the first byte of the VC-4 POH, and also to provide a justification opportunity for VC-4 (140Mbit/s) payloads.

The AU-4 is then mapped directly into an AUG or Administrative Unit Group, which then has the Section Overheads or SOH, added to it. These section overheads provide STM-1 framing, section performance monitoring and other maintenance functions pertaining to the section path. The VC-4 payload, plus AU pointers and Section Overheads, together form the complete STM-1 transport frame.

Because SDH can accept PCM signals at 140 Mbit/s directly into a VC-4 container there needs to be a mechanism to compensate for clock discrepancies between the SDH and PDH networks. The principles governing AU/VC-4 justification are identical to those of the lower order VC-12 signals. This justification process means that the VC-4 payload can move within the STM-1 frame format; therefore pointers are required to indicate the start of the VC-4.

The AU pointer bytes are part of the STM-1 section overheads and comprise of H1 and H2 as pointer indicators and H3 as the negative justification opportunity.

The H bytes are in multiples of three (to take into account AU-3 SONET mapping), but only the first byte of both the H1 and H2 bytes are used at VC-4 and the second and third bytes set to a null pointer indicator (NPI), a fixed bit pattern.

The pointer value is the offset between the end of the H3 byte and the start of the VC-4 POH i.e. from the end of H3 to the start of the J1 byte.

Because J1 can be anywhere (in-groups of three to take into account AU-3 SONET mapping), within the STM-1 payload area this AU pointer value can range from 0 to 782. The multiplexer will attempt to place the VC-4 frame at pointer value 522. This will fit the VC-4 directly into the STM-1 frame. There are occasions where due to justification processes the VC-4 will span across STM-1 frames.

As SDH caters for customer input rates of 140Mbit/s directly some form of justification is needed at the VC-4 level. This is achieved by using the 3 bytes of H3 and the next 3 bytes immediately following H3.

The justification takes place in frame number 3, of a 4 frame multiframe. Justification control is via a buffer system (as opposed to the control bits (C1, C2) in VC-12 justification). The incoming data is fed into a buffer. This buffer has two threshold levels. A 'low fill' level for slow rates and a 'high fill' threshold for fast data. When these thresholds are met, the H3 bytes and the 3 bytes immediately following are set accordingly.

If the customer data is being received at a faster rate than normal, the 3 bytes of H3 are used for customer data. This is known as negative justification.

STM-1 Section Overheads

The STM-1 Section Overhead (SOH) consists of nine columns by nine rows . It forms the start of the STM-1 frame. The SOH contains control and status messages (similar to the V5 and VC-4 POH) at the transmission section level.

The STM-1 section overhead is divided up into two parts.

The STM-1 Section Overhead (SOH) consists of nine columns by nine rows . It forms the start of the STM-1 frame. The SOH contains control and status messages (similar to the V5 and VC-4 POH) at the transmission section level.

The STM-1 section overhead is divided up into two parts.

➥The first is the Regenerator Section Overhead (RSOH).

➥The second is the Multiplexer Section Overhead (MSOH).

A1 & A2 - STM-1 Frame Alignment. These 6 bytes are used for STM-1 frame alignment. They are the first bytes transmitted. The A1 bytes have a value of F6 (hex) or binary 11110110. The A2 bytes have a value of 28 (hex) or binary 00101000. Frame alignment takes place over three STM-1 frames

J0 - STM-1 Section Path Trace. This byte is used to provide a fixed length user configurable string, which can be used to verify network topology connections. It is not supported by all manufactures.

E1 - Engineering Order Wire. This byte is used to provide a 64 kbit/s voice channel, within the regenerator section, for use in maintenance applications.

B2 - Byte Interleaved Parity Check 24 (BIP-24). These 3 bytes provide an error monitoring function for the STM-1 frame (excluding the RSOH), before scrambling. The frame is divided up into 3 byte chunks. Each chunk is then parity checked in the same manner as the BIP-8 check. The bit1 results are placed in the bit one's of the relevant BIP-24 byte. The bit2 results are placed in the bit two's of the relevant BIP-24 byte etc.

K1 - Automatic protection Switching (APS). This byte is used to perform automatic protection switching of the multiplexer section (MSP switching).

K2 - Automatic protection Switching (APS). This byte is used to convey a Multiplex Section Remote Defect Indication or MS RDI (formerly MS FERF).

D4 to D12 - Data Communications Channel (DCC). These 9 bytes provide a 576 kbit/s data channel for the use of network management systems.

0000 - indicates a quality unknown message.

0010 - indicates a G.811 Primary reference clock with an error rate of greater than 1x10-11 per day.

1011 - indicates a G.813 Internally generated reference clock.

1111 - indicates a 'Do not use for Synchronisation' message.

Z1, Z2 - Reserved. These four bytes are spare and reserved for future use.

M1 - Multiplex Section Remote Defect Indicator (MS RDI). This byte is used to convey back to the distant end a count of any errors detected by the BIP-24 error check. A value of 00000000 indicates zero errors. A value of 00011000 indicates an error count of 24 etc. This was formerly known as MS FEBE.

E2 - Engineering Order Wire. This byte is used to provide a 64 kbit/s voice channel, within the multiplexer section, for use in maintenance applications.

X - Reserved. These bytes are reserved for national use.

All unmarked bytes are reserved for future international standardisation.

2 Comments

54DA99BBBE

ReplyDeletekiralık hacker

hacker arıyorum

belek

kadriye

serik

CCF03F153B

ReplyDeleteInstagram Takipçi Hilesi

Tiktok Ücretsiz Beğeni

Twitter Ücretsiz Takipçi

Tumblr Beğeni Hilesi

SoundCloud Ücretsiz Beğeni

Threads Beğeni Hilesi

Twitch Ücretsiz Takipçi

Instagram Hikaye Görme

Instagram PP Büyütme